# Admont

This project has received funding from the ECSEL Joint Undertaking under grant agreement No 661796. This Joint Undertaking receives support from the European Union's Horizon 2020 research and innovation programme and Germany, Finland, Sweden, Italy, Austria, Hungary."

ADMONT

ADMONT Essential Capabilities & Services FhG-IZM/ASSIS Dresden

> Information for potential ADMONT pilot line user Status 07/2015

Advanced Distributed Pilot Line for More-than-Moore Technologies

# Who is ADMONT?

#### <u>Advanced Distributed Pilot Line for More-than-Moore Technologies</u>

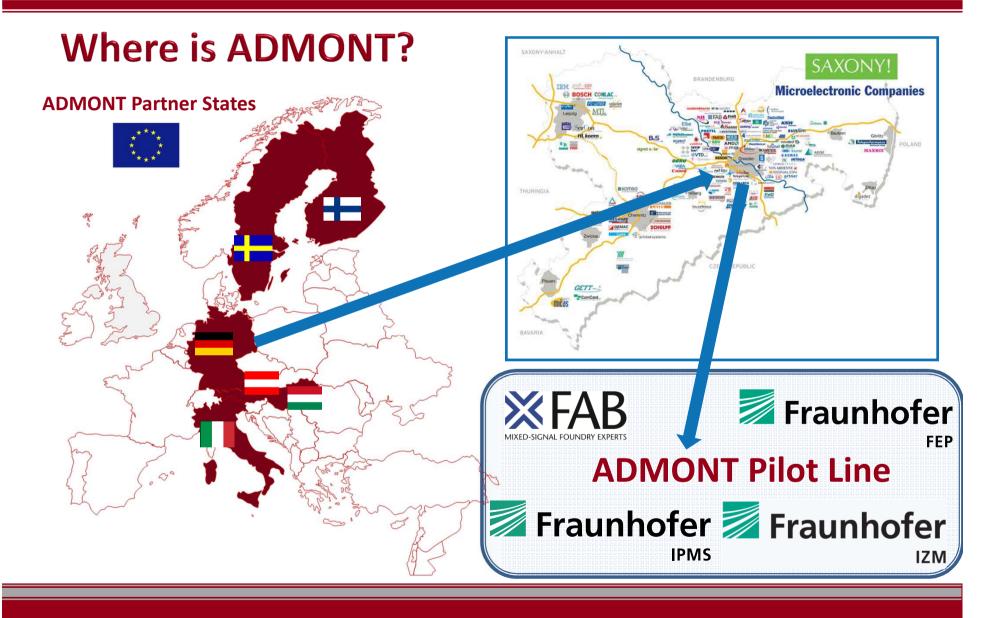

**ADMONT** is a **multi-KET pilot line** driven by a **combination** of **technology platforms** in Dresden carried by industry and research institutes serving pilot line clients in Europe

- ADMONT is organised along the **value chain** from wafer material, CMOS wafer, sensor and OLED processing to silicon system integration in one production flow

- ADMONT is an ECS (European Electronics Components and Systems) ecosystem in Saxony for Europe with sustainable impact on economic growth and employment in the European Union

- ADMONT addresses key applications: smart mobility, smart energy, smart health and smart production in excellent agreement with the ECSEL Multiannual Strategic Plan

- ADMONT addresses essential capabilities: **semiconductor process equipment** and **materials**, **design technology**, **smart system integration**

ADMONT as a distributed More-than-Moore pilot line is unique in Europe and worldwide.

# Admont

# Admont

# **ADMONT Concept & Capabilities**

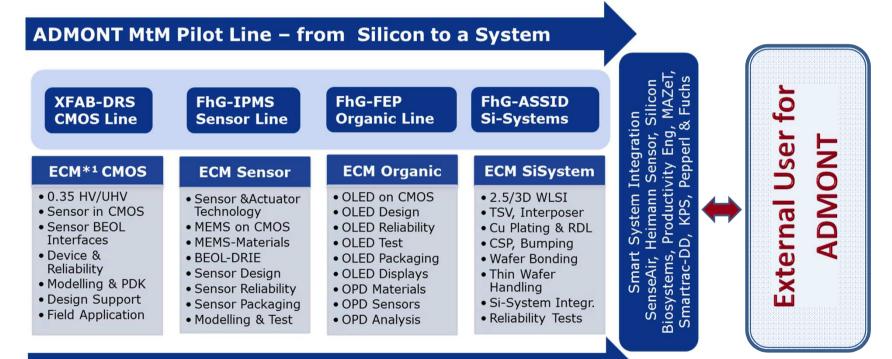

ADMONT pilot line concept, structure and excellences

#### Design: XFAB, PE, FhG-EAS, FhG-EMFT, FhG-FEP, IMMS, MAZeT, EDC

\*1 Essential Capability Modul

Detailed Information are available under (Link: XFAB, IPMS, FEP, ASSID)

8 July, 2015

# Fraunhofer IZM-ASSID Essential Capabilities

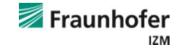

## **3D System Integration @ Fraunhofer IZM-ASSID**

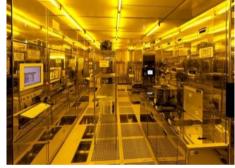

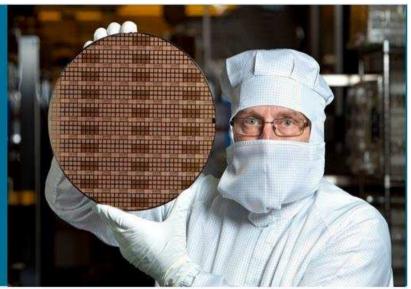

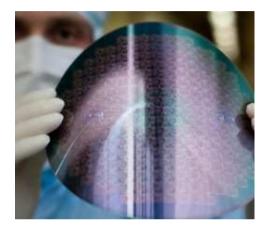

Fraunhofer IZM-ASSID operates a Leading Edge 300 mm Process Line for Wafer Level System Integration for process development, prototyping and manufacturing under industrycompatible conditions.

#### Facility & Infrastructure

Clean Room: 1100m<sup>2</sup>

Equipment for: Cu-TSV Formation, Re-distribution Layer, Bumping, 300 mm Wafer Thinning and Handling, 3D Stacking and Assembly, In-line Metrology and µ-Analysis

Contact: M. Jürgen Wolf +49 351/795572-12

wolf@izm.fraunhofer.de

All tool specifications are aligned to the requirements for specific applications and customer requests to 3D technology for TSV formation, silicon interposer and multifunctional device integration.

Tools are leading edge developments of selected supplier and aligned to process development, **prototyping and low volume manufacturing** under **industrial manufacturing conditions**.

Supported by

All Silicon System Integration Dresden - ASSID

### Fraunhofer IZM-ASSID Core Competencies

### **3D Wafer Level System Integration**

- Through Silicon Via (Cu-TSV) Formation

- Wafer Thinning, Thin Wafer Handling

- Wafer Bumping (SnAg, Cu-Pillar for 20nm node)

- TSV Interposer with High-density Redistribution Layers

- Assembly and Interconnection Technologies

ASSID – All Silicon System Integration Dresden

© Fraunhofer IZM

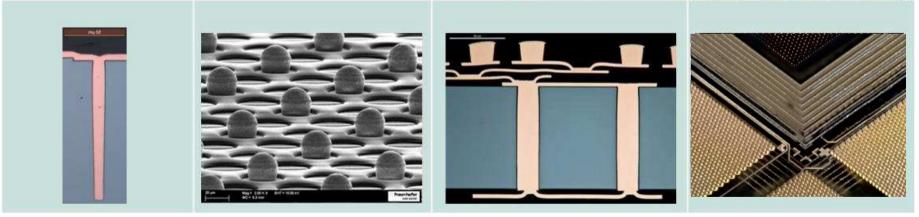

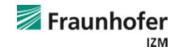

## **Through Silicon Via (TSV) Formation**

#### Capabilities

- Full Cu-TSV integration in active CMOS device wafers

- TSV process integration: via-middle/ via-last TSV, back side vialast

- Dry etch / wet cleaning

- Oxide liner deposition

- Barrier/seed-layer deposition (PVD), MOCVD, Ti, TiN, Ta, Cu

- TSV metallization : Cu-ECD

- Metal anneal up to 400°C

- Cu CMP / dielectric CMP

- Front side / back side contact formation

- TSV dimensions (diameter / depth):

- min. 5 μm / 60 μm

- typ. 10 μm / 100 μm

- 20 μm / 120μm

- Back side TSV (Cu-liner) up to 250 700 µm depth

back to overview

# Wafer Thinning / Thin Wafer Handling

#### Capabilities

#### Wafer Backgrinding

- Back grinding technologies:

- Grinding Before Dicing (GBD)

- Dicing before Grinding (DBG)

- 300 mm TAIKO Grinding

- Wafer Backgrinding/Polish of 300 (200) mm single wafers

- Rough grinding: mesh 320, mesh 600

- Fine grinding: mesh 1500, mesh 4000, mesh 6000

- Dry polish: Ra 0.0003µm, Ry = 0.0017µm

- Stress relief etch: SF6 or CF4 based

- Incoming wafer thickness: ≥ 500µm

- Outgoing wafer thickness: ≥ 50µm

- TTV: ≤ 5µm pending on wafer frontside topology

- Wafer Backgrinding/Polish of 300 (200)mm temporary bonded wafer stacks

- Rough grinding: mesh 320, mesh 600

- Fine grinding: mesh 1500, mesh 4000, mesh 6000

back to overview

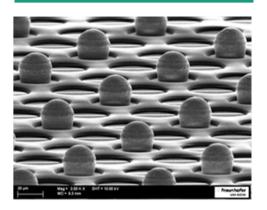

# Wafer Bumping

#### Capabilities

- Generation of mask design

- Application of photo polymer as protective layer

- Micro bumping on polymer ILD

- Micro bumping on I/O pad

- Copper bumping on polymer ILD

- Wafer dicing of bumped wafers

- Thinning of bumped wafers

- 2D/ 3D micro bump inspection (AOI) and mapping

- µ-Bump Materials

- Bump: Cu / SnAg

- Cu pillar bump

- Pad Modification: Cu/NiAu, Cu/Ni, Cu

- µ-Bump dimensions

- Bump Diameter: 25 μm / 13 μm

- Bump Pitch: 55 μm / 25 μm

- Bump Height: 30 μm / 15 μm

back to overview

# **TSV Interposer with high-density Redistribution Layers**

| IZM-ASSID |

|-----------|

|           |

#### Capabilities

- Customer specific design and prototyping based on IZM-ASSID design guidelines

- Fabrication of high density silicon interposer with TSV and multilayer redistribution

- Typical interposer features:

- TSV diameter: 10-20 μm

- TSV depth: > 100 µm

- multilayer redistribution layer on top and bottom side

- polymer and oxide dielectric and copper metallization

- Integration of passive elements e.g. R, L, (C)

- Development and verification of high density multi-layer RDL (polymer and oxide based) to replace high end organic substrates

- Application of interconnects micro bumps (Cu-Pillar, SnAg) for flip chip assembly

- Reliability assessment including thermomechanical and electrical characterization

## **Assembly and Interconnection Technologies**

#### Capabilities

#### Flip Chip Bonding

- Die-to-Wafer (D2W) Bonding

- Flux-activation or fluxless

- Dispensing Pre-applied underfill

- Inline or external reflow

- Die size: 3 30 mm

- Die thickness: ≥ 50 µm

- Minimum pitch: ≥ 45 µm

- Min. interconnect diameter: ≥ 25 µm

- Placement accuracy: 3 10 µm @3sigma

- Die feed: 300mm Plastic Film Frame Carrier (Disco Type), WafflePack or GelPack (no Flip)

#### Flip Chip Underfill Dispensing

- Dispensing of various underfill materials

- Total needle placement accuracy:  $\geq$  50µm @ 3sigma

- Different fluid pump systems (Line DU and Smart Stream)

- Edge Detection Vision Algorithm

- Automatic dispense mass calibration

- Height measurement sensor

- Substrate and needle heating

- Automatic needle cleaning and detection

- Maximum sample size (LxWxH): 300x300x50 resolution, 20 μm

#### www.izm.fraunhofer.de

Contact: M. Juergen Wolf wolf@izm.fraunhofer.de

# © Fraunhofer IZM

# **ADMONT Grant Agreement No. 661796**

"This project has received funding from the ECSEL Joint Undertaking under grant agreement No 661796.

This Joint Undertaking receives support from the European Union's Horizon 2020 research and innovation programme and Germany, Finland, Sweden, Italy, Austria, Hungary."

If you need further information, please contact the coordinator:

X-FAB Dresden GmbH & Co. KG

Grenzstrasse 28, 01109 Dresden, GERMANY

Tel: +49 351 40756 214 Fax: +49 351 40756 274

E-Mail: karl-heinz.stegemann@xfab.com

The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The users thereof use the information at their sole risk and liability.